# Condensed Notes On Digital Logics (According to BSeCSIT syllabus TU)

| ` | <br>- | J | <br>- 1 | <br>- / |

|---|-------|---|---------|---------|

|   |       |   |         |         |

|   |       |   |         |         |

|   |       |   |         |         |

By Bishnu Rawal

290

# Unit 1

# **Binary Systems**

#### Introduction

We are in "Information age" since digital systems have such a prominent and growing role in modern society. They are involved in our business transactions, communications, transportation, medical treatment and entertainment. In industrial world they are heavily employed in design, manufacturing, distribution and sales.

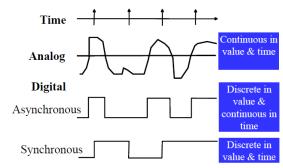

# Analog System

Analog systems process analog signals (continuous time signals) which can take any value within a range, for example the output from a speaker or a microphone.

An analog meter can display any value within the range available on its scale. However, the precision of readings is limited by our ability to read them. E.g. meter on the right shows 1.25V because the pointer is estimated to be half way between 1.2 and 1.3. The analogue meter can show any value between 1.2 and 1.3 but we are unable to read the scale more precisely than about half a division.

# **Digital System**

- Digital systems process digital signals which can take only a limited number of values (discrete steps), usually just two values are used: the positive supply voltage (+Vs) and zero volts (0V).

- Digital systems contain devices such as logic gates, flip-flops, shift registers and counters.

A digital meter can display many values, but not every value within its range. For example the display on the right can show 6.25 and 6.26 but not a value between them. This is not a problem because digital meters normally have sufficient digits to show values more precisely than it is possible to read an analogue display.

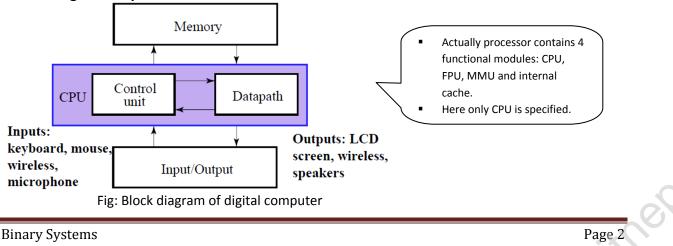

The general purpose digital computer is a best known example of **digital system**.

#### **Generic Digital computer structure**

**Working principle of generic digital computer**: Memory stores programs as well as input, output and intermediate data. The datapath performs arithmetic and other data-processing operations as specified by the program. The control unit supervises the flow of information between the various units. A datapath, when combined with the control unit, forms a component referred to as a *central processing unit,* or CPU. The program and data prepared by the user are transferred into memory by means of an input device such as a keyboard. An output device, such as a CRT (cathode-ray tube) monitor, displays the results of the computations and presents them to the user.

#### Advantages of digital system:

- Have made possible many scientific, industrial, and commercial advances that would have been unattainable otherwise.

- Less expensive

- More reliable

- Easy to manipulate

- Flexibility and Compatibility

- Information storage can be easier in digital computer systems than in analog ones. New features can often be added to a digital system more easily too.

#### Disadvantages of digital system:

- Use more energy than analog circuits to accomplish the same tasks, thus producing more heat as well.

- Digital circuits are often fragile, in that if a single piece of digital data is lost or misinterpreted, the meaning of large blocks of related data can completely change.

- Digital computer manipulates discrete elements of information by means of a binary code.

- Quantization error during analog signal sampling.

# **Information Representation**

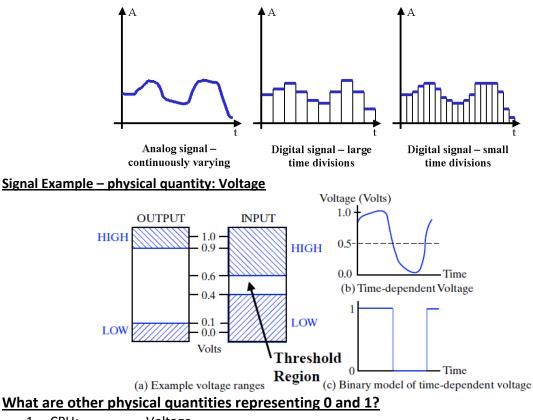

#### **Signals**

- Information variables represented by physical quantities.

- For digital systems, the variables take on discrete values.

- Two level or binary values are the most prevalent values in digital systems.

- Binary values are represented abstractly by:

- digits 0 and 1

- words (symbols) False (F) and True (T)

- words (symbols) Low (L) and High (H)

- and words On and Off.

- Binary values are represented by values or ranges of values of physical quantities

#### Signal Examples over time

Here is an example waveform of a quantized signal. Notice how the magnitude of the wave can only take certain values, and that creates a step-like appearance. This image is discrete in magnitude, but is continuous in time (asynchronous):

- 1. CPU: Voltage

- Disk: Magnetic Field Direction

- 2. CD: Surface Pits/Light

- Dynamic RAM: Electrical Charge

# **Number Systems**

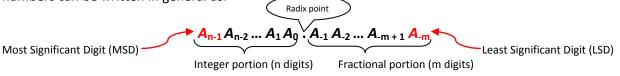

Here we discuss positional number systems with Positive radix (or base) r. A number with radix r is represented by a string of digits as below i.e. wherever you guys see numbers of whatever bases, all numbers can be written in general as:

in which  $\mathbf{0} \leq \mathbf{A}_i < \mathbf{r}$  (since each being a symbol for particular base system viz. for r = 10 (decimal number system)  $A_i$  will be one of 0,1,2,...,8,9). Subscript i gives the position of the coefficient and, hence, the weight  $r^i$  by which the coefficient must be multiplied.

**HEY!** Confused? Don't worry! I will describe specific number systems (r=2, 8, 10 and 16) used in digital computers later one by one, then the concept will be quite clear.

**Binary Systems**

By Bishnu Rawal

In general, a number in base *r* contains *r* digits, 0, l, 2... *r*- 1, and is expressed as a power series in *r* with the general form:

(Number)<sub>r</sub> =  $A_{n-1}r^{n-1} + A_{n-2}r^{n-2} + \dots + A_1r^1 + A_0r^0 + A_{-1}r^{-1} + A_{-2}r^{-2} + \dots + A_{-m+1}r^{-m+1} + A_{-m}r^{-m}$

$$(\text{Number})_{\mathbf{r}} = \left(\sum_{i=0}^{\mathbf{i}=\mathbf{n}-1} A_{\mathbf{i}} \cdot r^{\mathbf{i}}\right) + \left(\sum_{j=-\mathbf{m}}^{\mathbf{j}=-1} A_{\mathbf{j}} \cdot r^{\mathbf{j}}\right)$$

(Integer Portion) + (Fraction Portion)

#### Decimal Number System (Base-10 system)

Radix (r) = 10 Symbols = 0 through r-1 = 0 through 10-1 = {0, 1, 2... 8, 9}

I am starting from base-10 system since it is used vastly in everyday arithmetic besides computers to represent numbers by strings of digits or symbols defined above, possibly with a *decimal point*. Depending on its position in the string, each digit has an associated value of an integer raised to the power of 10.

Example: decimal number 724.5 is interpreted to represent 7 hundreds plus 2 tens plus 4 units plus 5 tenths.

$724.5 = 7 \times 10^{2} + 2 \times 10^{1} + 4 \times 10^{0} + 5 \times 10^{-1}$

#### Binary Number System (Base-2 system)

Radix (r) = 2 Symbols = 0 through r-1 = 0 through  $2-1 = \{0, 1\}$

A binary numbers are expressed with a string of 1'sand 0's and, possibly, a *binary point* within it. The decimal equivalent of a binary number can be found by expanding the number into a power series with a base of 2.

Example:  $(11010.01)_2$  can be interpreted using power series as:  $(11010.01)_2 = 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2} = (26.25)_{10}$

Digits in a binary number are called bits (**B**inary dig**IT**s). When a bit is equal to 0, it does not contribute to the sum during the conversion. Therefore, the conversion to decimal can be obtained by adding the numbers with powers of 2 corresponding to the bits that are equal to 1. Looking at above example,  $(11010.01)_2 = 16 + 8 + 2 + 0.25 = (26.25)_{10}$ .

In computer work,

- 2<sup>10</sup> is referred to as K (kilo),

- 2<sup>20</sup> as M (mega),

- 2<sup>30</sup> as G (giga),

- $2^{40}$  as T (tera) and so on.

| n | 2″  | n  | 2"     | n  | 2"        |

|---|-----|----|--------|----|-----------|

| 0 | 1   | 8  | 256    | 16 | 65,536    |

| 1 | 2   | 9  | 512    | 17 | 131,072   |

| 2 | 4   | 10 | 1,024  | 18 | 262,144   |

| 3 | 8   | 11 | 2,048  | 19 | 524,288   |

| 4 | 16  | 12 | 4,096  | 20 | 1,048,576 |

| 5 | 32  | 13 | 8,192  | 21 | 2,097,152 |

| 6 | 64  | 14 | 16,384 | 22 | 4,194,304 |

| 7 | 128 | 15 | 32,768 | 23 | 8,388,608 |

Table: Numbers obtained from 2 to the power of n

#### **Octal Number System (Base-8 system)**

Radix (r) = 8 Symbols = 0 through r-1 = 0 through 8-1 = {0, 1, 2...6, 7} An octal numbers are expressed with a strings of symbols defined above, possibly, an *octal point* within it. The decimal equivalent of a octal number can be found by expanding the number into a power series with a base of 8.

Example:  $(40712.56)_8$  can be interpreted using power series as:  $(40712.56)_8 = 4 \times 8^4 + 0 \times 8^3 + 7 \times 8^2 + 1 \times 8^1 + 2 \times 8^0 + 5 \times 8^{-1} + 6 \times 8^{-2} = (16842.1)_{10}$

#### Hexadecimal Number System (Base-16 system)

Radix (r) = 16 Symbols = 0 through r-1 = 0 through 16-1 = {0, 1, 2...9, A, B, C, D, E, F}

A hexadecimal numbers are expressed with a strings of symbols defined above, possibly, a *hexadecimal point* with in it. The decimal equivalent of a hexadecimal number can be found by expanding the number into a power series with a base of 16.

Example: (4D71B.C6)<sub>16</sub> can be interpreted using power series as:

$\begin{array}{rcl} (\text{4D71B.C6})_{16} & = & 4 \times 16^4 + \text{D} \times 16^3 + 7 \times 16^2 + 1 \times 16^1 + \text{B} \times 16^0 + \text{C} \times 16^{-1} + 6 \times 16^{-2} \\ & = & 4 \times 16^4 + 13 \times 16^3 + 7 \times 16^2 + 1 \times 16^1 + 11 \times 16^0 + 12 \times 16^{-1} + 6 \times 16^{-2} \\ & = & (317211.7734375)_{10} \end{array}$

# **Number Base Conversions**

**Case I:** <u>Base-r system to Decimal</u>: Base-r system can be binary (r=2), octal (r=8), hexadecimal (r=16), base-60 system or any other. For decimal system as destination of conversion, we just use power series explained above with varying r and sum the result according to the arithmetic rules of base-10 system. I have already done examples for binary to decimal, octal to decimal and hexadecimal to decimal.

For refreshment lets assume base-1000 number  $(458HQY)_{1000}$ . Where n = 6 and m = 0.  $(458HQY)_{1000} = A_{n-1}r^{n-1} + A_{n-2}r^{n-2} + ... + A_1r^1 + A_0r^0 + A_{-1}r^{-1} + A_{-2}r^{-2} + ... + A_{-m+1}r^{-m+1} + A_{-m}r^m$

$= 4 \times 1000^{5} + 5 \times 1000^{4} + 8 \times 1000^{3} + H \times 1000^{2} + Q \times 1000^{1} + Y \times 1000^{0}$

=Resulting number will be in decimal. Here I have supposed various symbols for base-1000 system. Don't worry, if someone gives you base-1000 number for conversion, he should also define all 1000 symbols (0-999).

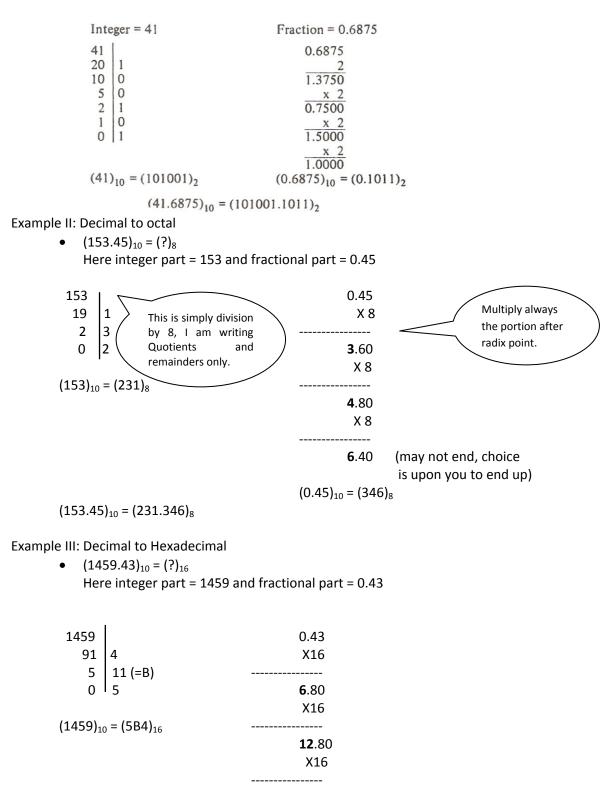

Case II: <u>Decimal to Base-r system</u>: Conversion follows following algorithm.

- 1. Separate the number into **integer** and **fraction** parts if radix point is given.

- 2. Divide "*Decimal Integer part*" by base *r* repeatedly until quotient becomes zero and storing remainders at each step.

- 3. Multiply "Decimal Fraction part" successively by r and accumulate the integer digits so obtained.

- 4. Combine both accumulated results and parenthesize the whole result with subscript *r*.

Example I: Decimal to binary

(41.6875)<sub>10</sub> = (?)<sub>2</sub>

Here Integer part = 41 and fractional part = 0.6875

**12**.80 (Never ending...) (0.43)<sub>10</sub> = (6CC)<sub>8</sub>

(1459.43)<sub>10</sub> = (5B4.6CC)<sub>16</sub>

Case III: Binary to octal & hexadecimal and vice-versa: Conversion from and to binary, octal and hexadecimal representation plays an important part in digital computers.

Since.

- $2^3$  = 8, octal digit can be represented by at least 3 binary digits. (We have discussed this much better in class). So to convert given binary number into its equivalent octal, we divide it into groups of 3 bits, give each group an octal symbol and combine the result.

- Integer part: Group bits from right to left of an octal point. O's can be added to make it multiple of 3 (not compulsory).

- Fractional part: Group bits from left to right of an octal point. O's must be added to if bits are not multiple of 3 (Note it).

- 24 = 16, each hex digit corresponds to 4 bits. So to convert given binary number into its ٠ equivalent hex, we divide it into groups of 4 bits, give each group a hex digit and combine the result. If hex point is given, then process is similar as of octal.

| Decimal<br>(base 10) | Binary<br>(base 2) | Octal<br>(base 8) | Hexadecima<br>(base 16) |

|----------------------|--------------------|-------------------|-------------------------|

| 00                   | 0000               | 00                | 0                       |

| 01                   | 0001               | 01                | 1                       |

| 02                   | 0010               | 02                | 2                       |

| 03                   | 0011               | 03                | 3                       |

| 04                   | 0100               | 04                | 4                       |

| 05                   | 0101               | 05                | 5                       |

| 06                   | 0110               | 06                | 6                       |

| 07                   | 0111               | 07                | 7                       |

| 08                   | 1000               | 10                | 8                       |

| 09                   | 1001               | 11                | 9                       |

| 10                   | 1010               | 12                | A                       |

| 11                   | 1011               | 13                | В                       |

| 12                   | 1100               | 14                | С                       |

| 13                   | 1101               | 15                | D                       |

| 14                   | 1110               | 16                | E                       |

| 15                   | 1111               | 17                | F                       |

15 numbers in 4 systems summarized below for easy reference. •

Example:

- 1. Binary to octal:  $(10110001101011.11110000011)_2 = (010 10 01 101 011 01 011 011 010 000 110)_2 = (26153.7406)_8$

- 2. Binary to hexadecimal:  $(10110001101011.11110000011)_2 = (0010, 1100, 0110, 1011, 1111, 0000, 0110)_2 = (2C6B.F06)_{16}$ 6 B F 2 C

- 3. From hex & octal to binary is quite easy, we just need to remember the binary of particular hex or octal digit.

$(673.12)_8 = 110 \ 111 \ 011. \ 001 \ 010 = (110111011.00101)_2$  $(3A6.C)_{16} = 0011\ 1010\ 0110.\ 1100 = (1110100110.11)_2$

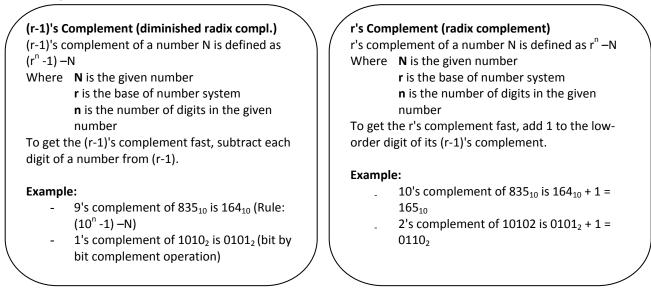

# Complements

Complements are used in digital computers for simplifying the subtraction operation and for logical manipulation. There are two types of complements for each base-r system: r's complement and the second as the (r - 1)'s complement. When the value of the base r is substituted, the two types are referred to as the 2's complement and 1's complement for binary numbers, the 10's complement and 9's complement for decimal numbers etc.

# Subtraction with complements

The direct method of subtraction taught in elementary schools uses the borrow concept. When subtraction is implemented with digital hardware, this method is found to be less efficient than the method that uses complements.

The subtraction of two n-digit unsigned numbers *M* - *N* in base-*r* can be done as follows:

- 1. Add the minuend M to the r's complement of the subtrahend N. This performs  $M + (r^n N) = M N + r''$ .

- 2. If  $M \ge N$ , the sum will produce an end carry, r'', which is discarded; what is left is the result M N.

- 3. If M < N, the sum does not produce an end carry and is equal to  $r^n (N M)$ , which is the *r*'s complement of (N M). To obtain the answer in a familiar form, take the r's complement of the sum and place a negative sign in front.

Example I:

Using 10's complement, subtract 72532 - 3250.

|                            | /       |

|----------------------------|---------|

| M =                        | 72532   |

| 10's complement of $N =$   | + 96750 |

| Sum =                      | 169282  |

| Discard end carry $10^5 =$ | -100000 |

| Answer =                   | 69282   |

**HEY!** *M* has 5 digits and *N* has only 4 digits. Both numbers must have the same number of digits; so we can write *N* as 03250. Taking the 10's complement of *N* produces a 9 in the most significant position. The occurrence of the end carry signifies that  $M \ge N$  and the result is positive. Example II: Using 10's complement, subtract 3250 - 72532.

| M =                      | 03250   |

|--------------------------|---------|

| 10's complement of $N =$ | + 27468 |

| Sum =                    | 30718   |

| There is no end carry.   |         |

Answer:

$$-(10$$

's complement of  $30718) = -69282$

Example III:

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a) X - Y and (b) Y - X using 2's complements.

| (a) | X =                       | 1010100           |

|-----|---------------------------|-------------------|

|     | 2's complement of $Y =$   | + 0111101         |

|     | Sum =                     | 10010001          |

|     | Discard end carry $2^7 =$ | - <u>10000000</u> |

|     | Answer: $X - Y =$         | 0010001           |

| (b) | Y =                       | 1000011           |

|     | 2's complement of $X =$   | + 0101100         |

|     | Sum =                     | 1101111           |

|     | There is no end carry.    |                   |

Answer: Y - X = -(2's complement of 1101111) = -0010001

Example IV: Repeating Example III using 1's complement.

(a)

$$X - Y = 1010100 - 1000011$$

$X = 1010100$

1's complement of  $Y = + 0111100$

Sum = 10010000

End-around carry  $\rightarrow + 1$

Answer:  $X - Y = 0010001$

(b)  $Y - X = 1000011 - 1010100$

$Y = 1000011$

1's complement of  $X = + 0101011$

Sum = 1101110

There is no end carry.

Answer: Y - X = -(1's complement of 1101110) = -0010001

**Binary Systems**

20

# **Binary Codes**

Electronic digital systems use signals that have two distinct values and circuit elements that have two stable states. There is a direct analogy among binary signals, binary circuit elements, and binary digits. A binary number of n digits, for example, may be represented by n binary circuit elements, each having an output signal equivalent to a 0 or a 1. Digital systems represent and manipulate not only binary numbers, but also many other discrete elements of information. Any discrete element of information distinct among a group of quantities can be represented by a binary code. Binary codes play an important role in digital computers. The codes must be in binary because computers can only hold 1's and 0's.

# 1. Binary Coded Decimal (BCD)

The binary number system is the most natural system for a computer, but people are accustomed to the decimal system. So, to resolve this difference, computer uses decimals in coded form which the hardware understands. A binary code that distinguishes among 10 elements of decimal digits must contain at least four bits. Numerous different binary codes can be obtained by arranging four bits into 10 distinct combinations. The code most commonly used for the decimal digits is the straightforward binary assignment listed in the table below. This is called **binary-coded decimal** and is commonly referred to as **BCD**.

| Decimal<br>Symbol     | BCD<br>Digit         |                                                                   |

|-----------------------|----------------------|-------------------------------------------------------------------|

|                       |                      | • A number with <i>n</i> decimal digits will require 4n bits      |

| 0                     | 0000                 | in BCD. E.g. decimal 396 is represented in BCD                    |

| 1                     | 0001                 | with 12 bits as 0011 1001 0110.                                   |

| 2                     | 0010                 | <ul> <li>Numbers greater than 9 has a representation</li> </ul>   |

| 3                     | 0011                 | different from its equivalent binary number, even                 |

| 4                     | 0100                 | though both contain 1's and 0's.                                  |

| 5                     | 0101                 | <ul> <li>Binary combinations 1010 through 1111 are not</li> </ul> |

| 6                     | 0110                 | used and have no meaning in the BCD code.                         |

| 7                     | 0111                 | • Example:                                                        |

| 8                     | 1000                 | (105) = (0001 1000 0101) = (10111001)                             |

| 9                     | 1001                 | $(185)_{10} = (0001\ 1000\ 0101)_{BCD} = (10111001)_2$            |

| Table: 4-bit BCD code | e for decimal digits |                                                                   |

#### 2. Error-Detection codes

Binary information can be transmitted from one location to another by electric wires or other communication medium. Any external noise introduced into the physical communication medium may change some of the bits from 0 to 1 or vice versa.

The purpose of an error-detection code is to detect such bit-reversal errors. One of the most common ways to achieve error detection is by means of a **parity bit**. A *parity bit* is the extra bit included to make the total number of 1's in the resulting code word either even or odd. A message of 4-bits and a parity bit P are shown in the table below:

e ?

| Odd parity |       | Ddd parity Even parity |     |

|------------|-------|------------------------|-----|

| Message    | <br>P | Message                | P   |

| 0000       | 1     | 0000                   | 0   |

| 0001       | 0     | 0001                   | 1   |

| 0010       | 0     | 0010                   | 1   |

| 0011       | 1     | 0011                   | 0   |

| 0100       | 0     | 0100                   | 1   |

| 0101       | 1     | 0101                   | - 0 |

| 0110       | 1     | 0110                   | 0   |

| 0111       | 0     | 0111                   | 1   |

| 1000       | 0     | 1000                   | 1   |

| 1001       | 1     | 1001                   | 0   |

| 1010       | 1     | 1010                   | 0   |

| 1011       | 0     | 1011                   | 1   |

| 1100       | 1     | 1100                   | 0   |

| 1101       | 0     | 1101                   | 1   |

| 1110       | 0     | 1110                   | -1  |

| 1111       | 1     | 1111                   | 0   |

#### **Error Checking Mechanism:**

$\rightarrow$ During the transmission of information from one location to another, an even parity bit is generated in the sending end for each message transmission. The message, together with the parity bit, is transmitted to its destination. The parity of the received data is checked in the receiving end. If the parity of the received information is not even, it means that at least one bit has changed value during the transmission.

$\rightarrow$  This method detects one, three, or any odd combination of errors in each message that is transmitted. An even combination of errors is undetected. Additional error-detection schemes may be needed to take care of an even combination of errors.

#### 3. Gray code (Reflected code)

It is a binary coding scheme used to represent digits generated from a mechanical sensor that may be prone to error. Used in telegraphy in the late 1800s, and also known as "reflected binary code". Gray code was patented by Bell Labs researcher Frank Gray in 1947. In Gray code, there is **only one bit location different between two successive values**, which makes mechanical transitions from one digit to the next less error prone. The following chart shows normal binary representations from 0 to 15 and the corresponding Gray code.

| Decimal digit | Binary code | Gray code |

|---------------|-------------|-----------|

| 0             | 0000        | 0000      |

| 1             | 0001        | 0001      |

| 2             | 0010        | 0011      |

| 3             | 0011        | 0010      |

| 4             | 0100        | 0110      |

| 5             | 0101        | 0111      |

| 6             | 0110        | 0101      |

| 7             | 0111        | 0100      |

| 8             | 1000        | 1100      |

| 9             | 1001        | 1101      |

| 10            | 1010        | 1111      |

| 11            | 1011        | 1110      |

| 12            | 1100        | 1010      |

| 13            | 1101        | 1011      |

| 14            | 1110        | 1001      |

| 15            | 1111        | 1000      |

|               |             |           |

The Gray code is used in applications where the normal sequence of binary numbers may produce an error or ambiguity during the transition from one number to the next. If binary numbers are used, a change from 0111 to 1000 may produce an intermediate erroneous number 1001 if the rightmost bit takes more time to change than the other three bits. The Gray code eliminates this problem since only one bit changes in value during any transition between two numbers.

#### 4. Alphanumeric codes

Alphanumeric character set is a set of elements that includes the 10 decimal digits, 26 letters of the alphabet and special characters such as \$, %, + etc. It is necessary to formulate a binary code for this set to handle different data types. If only capital letters are included, we need a binary code of at least six bits, and if both uppercase letters and lowercase letters are included, we need a binary code of at least seven bits.

#### • ASCII character code

The standard binary code for the alphanumeric characters is called ASCII (American Standard Code for Information Interchange). It uses seven bits to code 128 characters as shown in the table below. The seven bits of the code are designated by  $B_1$  through  $B_7$  with  $B_7$  being the most significant bit.

|                |      |     |     | ${\bf B}_7 {\bf B}_6 {\bf B}_9$ | 5   |     |     |     |                |

|----------------|------|-----|-----|---------------------------------|-----|-----|-----|-----|----------------|

| $B_4B_3B_2B_1$ | 000  | 001 | 010 | 011                             | 100 | 101 | 110 | 111 |                |

| 0000           | NULL | DLE | SP  | 0                               | @   | Р   |     | р   |                |

| 0001           | SOH  | DC1 | !   | 1                               | A   | Q   | a   | q   | NOTE:          |

| 0010           | STX  | DC2 |     | 2                               | в   | R   | b   | r   | Decimal digit  |

| 0011           | ETX  | DC3 | #   | 3                               | С   | S   | с   | S   | 0              |

| 0100           | EOT  | DC4 | \$  | 4                               | D   | Т   | d   | t   | in ASCII can b |

| 0101           | ENQ  | NAK | %   | 5                               | E   | U   | e   | u   | converted t    |

| 0110           | ACK  | SYN | &   | 6                               | F   | v   | f   | v   | BCD b          |

| 0111           | BEL  | ETB | ,   | 7                               | G   | W   | g   | w   |                |

| 1000           | BS   | CAN | (   | 8                               | Н   | X   | h   | x   | removing th    |

| 1001           | HT   | EM  | )   | 9                               | I   | Y   | i   | у   | three highe    |

| 1010           | LF   | SUB |     | :                               | J   | Z   | j   | Z   | order bit      |

| 1011           | VT   | ESC | +   | ;                               | K   | [   | k   | 1   |                |

| 1100           | FF   | FS  | ,   | <                               | L   | 1   | 1   | Í.  | 011.           |

| 1101           | CR   | GS  | -   | =                               | Μ   | ]   | m   | }   |                |

| 1110           | SO   | RS  |     | >                               | N   | ~   | n   | ~   |                |

| 1111           | SI   | US  | 1   | ?                               | 0   |     | 0   | DEL |                |

#### American Standard Code for Information Interchange (ASCII)

#### Various control character symbolic notation stands for:

| NULL | NULL                | DLE | Data link escape          |

|------|---------------------|-----|---------------------------|

| SOH  | Start of heading    | DC1 | Device control 1          |

| STX  | Start of text       | DC2 | Device control 2          |

| ETX  | End of text         | DC3 | Device control 3          |

| EOT  | End of transmission | DC4 | Device control 4          |

| ENQ  | Enquiry             | NAK | Negative acknowledge      |

| ACK  | Acknowledge         | SYN | Synchronous idle          |

| BEL  | Bell                | ETB | End of transmission block |

| BS   | Backspace           | CAN | Cancel                    |

| HT   | Horizontal tab      | EM  | End of medium             |

| LF   | Line feed           | SUB | Substitute                |

| VT   | Vertical tab        | ESC | Escape                    |

| FF   | Form feed           | FS  | File separator            |

| CR   | Carriage return     | GS  | Group separator           |

| SO   | Shift out           | RS  | Record separator          |

| SI   | Shift in            | US  | Unit separator            |

| SP   | Space               | DEL | Delete                    |

Example: ASCII for each symbol is  $(B_7B_6B_5B_4B_3B_2B_1)$ G  $\leftarrow$  100 0111, (  $\leftarrow$  010 1000, h  $\leftarrow$  110 1000, >  $\leftarrow$  011 1110 and so on.

eR

#### • EBCDIC character code

EBCDIC (Extended Binary Coded Decimal Interchange Code) is another alphanumeric code used in IBM equipment. It uses **eight bits** for each character. EBCDIC has the same character symbols as ASCII, but the bit assignment for characters is different. As the name implies, the binary code for the letters and numerals is an extension of the binary-coded decimal (BCD) code. This means that the last four bits of the code range from 0000 though 1001 as in BCD.

# Integrated Circuits (ICs)

An Integrated circuit is an association (or connection) of various electronic devices such as resistors, capacitors and transistors etched (or fabricated) to a semiconductor material such as silicon or germanium. It is also called as a **chip** or **microchip**. An IC can function as an amplifier, rectifier, oscillator, counter, timer and memory. Sometime ICs are connected to various other systems to perform complex functions.

#### Types of ICs

ICs can be categorized into two types

- Analog or Linear ICs

- Digital or logic ICs

Further there are certain ICs which can perform as a combination of both analog and digital functions.

**Analog or Linear ICs:** They produce continuous output depending on the input signal. From the name of the IC we can deduce that the output is a linear function of the input signal. Op-amp (operational amplifier) is one of the types of linear ICs which are used in amplifiers, timers and counters, oscillators etc.

**Digital or Logic ICs**: Unlike Analog ICs, Digital ICs never give a continuous output signal. Instead it operates only during defined states. Digital ICs are used mostly in microprocessor and various memory applications. Logic gates are the building blocks of Digital ICs which operate either at 0 or 1.

#### Advantages of ICs

- In consumer electronics, ICs have made possible the development of many new products, including personal calculators and computers, digital watches, and video games.

- They have also been used to improve or lower the cost of many existing products, such as appliances, televisions, radios, and high-fidelity equipment.

- The logic and arithmetic functions of a small computer can now be performed on a single VLSI chip called a microprocessor.

- Complete logic, arithmetic, and memory functions of a small computer can be packaged on a single printed circuit board, or even on a single chip.

#### **Levels of Integration**

During 1959 two different scientists invented IC's. Jack Kilby from Texas Instruments made his first germanium IC during 1959 and Robert Noyce made his first silicon IC during the same year. But ICs were not the same since the day of their invention; they have evolved a long way. Integrated circuits are often classified by the number of transistors and other electronic components they contain:

- SSI (small-scale integration): Up to 100 electronic components per chip

- MSI (medium-scale integration): From 100 to 3,000 electronic components per chip

28

- LSI (large-scale integration): From 3,000 to 100,000 electronic components per chip

- VLSI (very large-scale integration): From 100,000 to 1,000,000 electronic components per chip

- ULSI (ultra large-scale integration): More than 1 million electronic components per chip

# SIP (Single In-line Package) and DIP (Dual In-line Package) SIP

A **single in-line package** is an electronic device package which has one row of connecting pins. It is not as popular as the dual in-line package (DIP) which contains two rows of pins, but has been used for packaging RAM chips and multiple resistors with a common pin. SIPs group RAM chips together on a small board. The board itself has a single row of pin-leads that resembles a comb extending from its bottom edge, which plug into a special socket on a system or system-expansion board. SIPs are commonly found in memory modules. SIP is not to be confused with SIPP which is an archaic term referring to Single In-line Pin Package which was a memory used in early computers.

#### DIP

Dual in-line package (DIP) is a type of semiconductor component packaging. DIPs can be installed either in sockets or permanently soldered into holes extending into the surface of the printed circuit board. DIP is relatively broadly defined as any rectangular package with two uniformly spaced parallel rows of pins pointing downward, whether it contains an IC chip or some other device(s), and whether the pins emerge from the sides of the package and bend downwards. A DIP is usually referred to as a **DIP***n*, where *n* is the total number of pins.

For example, a microcircuit package with two rows of seven vertical leads would be a DIP14. The photograph below shows three DIP14 ICs.

Several DIP variants for ICs exist, mostly distinguished by packaging material:

- Ceramic Dual In-line Package (CERDIP or CDIP)

- Plastic Dual In-line Package (PDIP)

- Shrink Plastic Dual In-line Package (SPDIP) -A denser version of the PDIP with a 0.07 in. (1.778 mm) lead pitch.

- Skinny Dual In-line Package (SDIP) Sometimes used to refer to a 0.3 in. wide DIP, normally when clarification is needed e.g. for a 24 or 28 pin DIP.

By Bishnu Rawal

Fig: Several PDIPs and CERDIPs. The large CERDIP in the foreground is an Intel 8080 microprocessor.

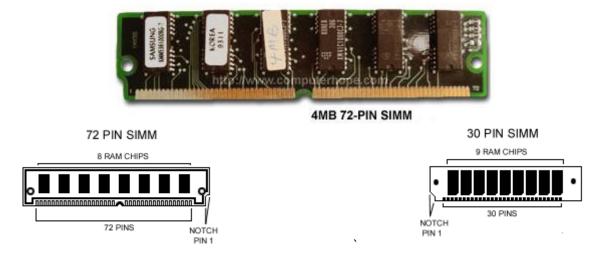

#### SIMM (Single In-line Memory Module) and DIMM (Dual In-line Memory Module)

Theses two terms (SIMM and DIMM) refer to a way series of dynamic random access memory integrated circuits modules are mounted on a printed circuit board and designed for use in personal computers, workstations and servers.

#### SIMM

Short for **Single In-line Memory Module, SIMM** is a circuit board that holds six to nine memory chips per board, the ninth chip usually an error checking chip (parity/non parity) and were commonly used with Intel Pentium or Pentium compatible motherboards. SIMMs are rarely used today and have been widely replaced by DIMMs. SIMMs are available in two flavors: 30 pin and 72 pin. 30-pin SIMMs are the older standard, and were popular on third and fourth generation motherboards. 72-pin SIMMs are used on fourth, fifth and sixth generation PCs.

#### DIMM

Short for **Dual In-line Memory Module, DIMM** is a circuit board that holds memory chips. DIMMs have a 64-bit path because of the Pentium Processor requirements. Because of the new bit path, DIMMs can be installed one at a time, unlike SIMMs on a Pentium that would require two to be added. Below is an example image of a 512MB DIMM memory stick.

**SO-DIMM** is short for **Small Outline DIMM** and is available as a 72-pin and 144-pin configuration. SO-DIMMs are commonly utilized in laptop computers.

Some of the advantages DIMMs have over SIMMs:

- DIMMs have separate contacts on each side of the board, thereby providing twice as much data as a single SIMM.

- The command address and control signals are buffered on the DIMMs. With heavy memory requirements this will reduce the loading effort of the memory.

# Description of a few types of chips (Just for Knowledge, not in syllabus)

**CMOS:** in computer science, acronym for complementary metal-oxide semiconductor. A semiconductor device that consists of two metal-oxide semiconductor field effect transistors (MOSFETs), one N-type and one P-type, integrated on a single silicon chip. Generally used for RAM and switching applications, these devices have very high speed and extremely low power consumption. They are, however, easily damaged by static electricity.

**Digital Signal Processor (DSP)**: An integrated circuit designed for high-speed data manipulations, used in audio, communications, image manipulation, and other data-acquisition and data-control applications.

**Dynamic RAM (DRAM)**: In computer science, a form of semiconductor random access memory (RAM). Dynamic RAMs store information in integrated circuits that contain capacitors. Because capacitors lose their charge over time, dynamic RAM boards must include logic to "refresh" (recharge) the RAM chips continuously. While a dynamic RAM is being refreshed, it cannot be read by the processor; if the processor must read the RAM while it is being refreshed, one or more wait states occur. Because their internal circuitry is simple, dynamic RAMs are more commonly used than static RAMs, even though they are slower. A dynamic RAM can hold approximately four times as much data as a static RAM chip of the same complexity.

**EPROM**: In computer science, acronym for erasable programmable read-only memory, also called reprogrammable read-only memory (RPROM). EPROMs are nonvolatile memory chips that are programmed after they are manufactured. EPROMs are a good way for hardware vendors to put variable or constantly changing code into a prototype system when the cost of producing many PROM chips would be prohibitive. EPROMs differ from PROMs in that they can be erased, generally by removing a protective cover from the top of the chip package and exposing the semiconductor material to ultraviolet light, and can be reprogrammed after having been erased. Although EPROMs are more expensive than PROMs, they can be more cost-effective in the long run if many changes are needed.

**PROM**: Acronym for programmable read-only memory. In computer science, a type of read-only memory (ROM) that allows data to be written into the device with hardware called a PROM programmer. After a PROM has been programmed, it is dedicated to that data, and it cannot be

reprogrammed. Because ROMs are cost-effective only when produced in large volumes, PROMs are used during the prototyping stage of the design. New PROMs can be created and discarded as needed until the design is perfected.

**Reduced Instruction Set Computer (RISC)**: Type of microprocessor that focuses on rapid and efficient processing of a relatively small set of instructions. RISC design is based on the premise that most of the instructions a computer decodes and executes are simple. As a result, RISC architecture limits the number of instructions that are built into the microprocessor but optimizes each so it can be carried out very rapidly-usually within a single clock cycle. RISC chips thus execute simple instructions faster than microprocessors designed to handle a much wider array of instructions.

**ROM:** Acronym for read-only memory. In computer science, semiconductor-based memory that contains instructions or data that can be read but not modified. To create a ROM chip, the designer supplies a semiconductor manufacturer with the instructions or data to be stored; the manufacturer then produces one or more chips containing those instructions or data. Because creating ROM chips involves a manufacturing process, it is economically viable only if the ROM chips are produced in large quantities; experimental designs or small volumes are best handled using PROM or EPROM. In general usage, the term ROM often means any read-only device, including PROM and EPROM.

**Static RAM (SRAM):** In computer science, a form of semiconductor memory (RAM). Static RAM storage is based on the logic circuit known as a flip-flop, which retains the information stored in it as long as there is enough power to run the device. A static RAM chip can store only about one-fourth as much data as a dynamic RAM chip of the same complexity, but static RAM does not require refreshing and is usually much faster than dynamic RAM. It is also more expensive. Static RAMs are usually reserved for use in caches.

(eX-

# Unit 2

# **Boolean algebra and Logic Gates**

Before starting the discussion of Boolean algebra and complex logic gates (NAND, XOR etc), let me describe bit about the binary logic (which you guys have studied in discrete structure course) and how this logic is implemented in hardware using basic gates?

#### **Binary logic**

Binary logic consists of binary variables and logical operations. The variables are designated by letters of the alphabet such as *A*, *B*, *C*, *x*, *y*, *Z*, etc., with each variable having two and only two distinct possible values: 1 and 0. There are three basic logical operations: AND, OR, and NOT.

- 1. AND: This operation is represented by a dot or by the absence of an operator. For example, x.y = z or xy = z is read "x AND y is equal to z." The logical operation AND is interpreted to mean that z = 1 if and only if x = 1 and y = 1; otherwise z = 0. (Remember that x, y, and z are binary variables and can be equal either to 1 or 0, and nothing else.)

- 2. OR: This operation is represented by a plus sign. For example, x + y = z is read "x OR y is equal to z," meaning that z = 0 if x = 0 or if y = 0 otherwise z = 1.

- 3. NOT: This operation is represented by a prime (sometimes by a bar). For example, x' = z is read "not x is equal to z," meaning that z is what x is not. In other words, if x = 1, then z = 0; but if x = 0, then z = 1.

These definitions may be listed in a compact form using truth tables. A **truth table** is a table of all possible combinations of the variables showing the relation between the values that the variables may take and the result of the operation.

| AND |    | OR  |       | NOT |   |

|-----|----|-----|-------|-----|---|

| х у | xy | х у | x + y | x   | x |

| 0 0 | 0  | 0 0 | 0     | 0   | 1 |

| 0 1 | 0  | 0 1 | 1     | 1   | 0 |

| 1 0 | 0  | 1 0 | 1     |     |   |

| I 1 | 1  | 11  | 1     |     |   |

**HEY!** Binary logic should not be confused with binary arithmetic (However we use same symbols here). You should realize that an arithmetic variable designates a number that may consist of many digits. A logic variable is always either 1 or 0. For example, in binary arithmetic, 1 + 1 = 10 (read: "one plus one is equal to 2"), whereas in binary logic, we have 1 + 1 = 1 (read: "one OR one is equal to one").

#### Switching circuits and Binary Signals

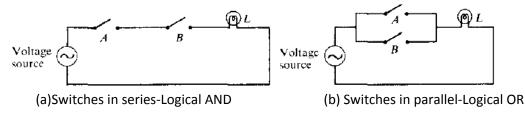

The use of binary variables and the application of binary logic are demonstrated by the simple switching circuits shown below:

Page 1

Let the manual switches A and B represent two binary variables with values equal to 0 when the switch is open and 1 when the switch is closed. Similarly, let the lamp L represent a third binary variable equal to 1 when the light is on and 0 when off.

Electronic digital circuits are sometimes called **switching circuits** because they behave like a switch, with the active element such as a transistor either conducting (switch closed) or not conducting (switch open). Instead of changing the switch manually, an electronic switching circuit uses **binary signals** to control the conduction or non-conduction state of the transistor.

# Basic Logic Gates (Digital logic gates will be covered in detail later)

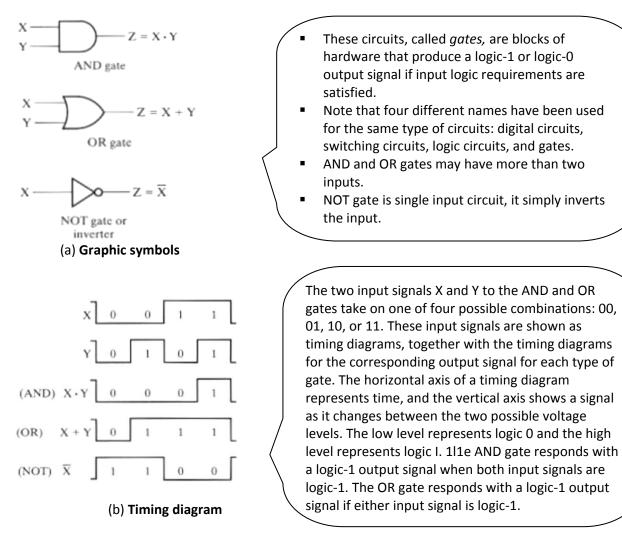

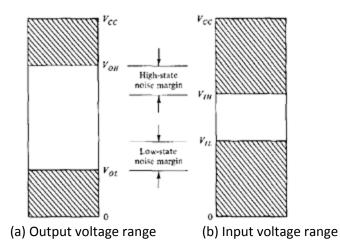

Logic gates are electronic circuits that operate on one or more input signals to produce an output signal. Electrical signals such as voltages or currents exist throughout a digital system in either one of two recognizable values (bi-state 0 or 1). Voltage-operated circuits respond to two separate voltage ranges (Example of voltage ranges is discussed in unit 1) that represent a binary variable equal to logic 1 or logic 0. The graphics symbols used to designate the three types of gates AND, OR, and NOT are shown in Figure below:

#### **Boolean algebra**

In 1854 George Boole introduced a systematic treatment of logic and developed for this purpose an algebraic system now called *Boolean algebra*. In 1938 C. E. Shannon introduced a two-valued Boolean algebra called *switching algebra*, in which he demonstrated that the properties of bistable electrical switching circuits can be represented by this algebra.

Thus, the mathematical system of binary logic is known as **Boolean or switching algebra**. This algebra is conveniently used to describe the operation of complex networks of digital circuits. Designers of digital systems use Boolean algebra to transform circuit diagrams to algebraic expressions and vice versa. For any given algebra system, there are some initial assumptions, or postulates, that the system follows. We can deduce additional rules, theorems, and other properties of the system from this basic set of postulates. Boolean algebra systems often employ the postulates formulated by E. V. Huntington in 1904.

#### Postulates

Boolean algebra is an algebraic structure defined on a set of elements *B* (*Boolean system*) together with two binary operators + (OR) and  $\bullet$  (AND) and unary operator ' (NOT), provided the following postulates are satisfied:

P1→ Closure: Boolean algebra is closed under the AND, OR, and NOT operations.

**P2→ Commutativity:** The • and + operators are commutative i.e. x + y = y + x and x • y = y • x, for all  $x, y \in B$ .

**P3→ Distribution:** • and + are distributive with respect to one another i.e.

$$x \bullet (y + z) = (x \bullet y) + (x \bullet z).$$

$x+(y\bullet z)=(x+y)\bullet(x+z),\,for\,all\,x,\,y,\,z\in\mathsf{B}.$

**P4** Hentity: The identity element with respect to • is 1 and + is 0 i.e. x + 0 = 0 + x = x and x • 1 = 1 • x = x. There is no identity element with respect to logical NOT.

**P5** Inverse: For every value x there exists a value x' such that  $x \bullet x' = 0$  and x + x' = 1. This value is the logical complement (or NOT) of x.

**P6** There exists at least two elements  $x, y \in B$  such that  $x \neq y$ .

One can formulate many Boolean algebras (viz. set theory, n-bit vectors algebra), depending on the choice of elements of B and the rules of operation. Here, we deal only with a two-valued Boolean algebra, i.e.,  $B = \{0, 1\}$ . Two-valued Boolean algebra has applications in set theory and in propositional logic. Our interest here is with the application of Boolean algebra to gate-type circuits.

#### **Basic theorems and Properties of Boolean algebra**

#### Duality

Postulates of Boolean algebra are found in pairs; one part may be obtained from the other if the binary operators and the identity elements are interchanged. This important property of Boolean algebra is called the **duality principle**. It states that *"Every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operators and identity elements are interchanged"*. In a two-valued Boolean algebra, the identity elements and the elements of the set *B* are the same: 1 and 0. If the *dual* of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

éR

#### **Basic theorems**

The theorems, like the postulates, are listed in pairs; each relation is the dual of the one paired with it. The postulates are basic axioms of the algebraic structure and need no proof. The theorems must be proven from the postulates. six theorems of Boolean algebra are given below:

```

Theorem1:

Idempotence (a) x + x = x

(b) x.x = x

Theorem2:

(b) x.0 = 0

Existence: 0\&1 (a) x + 1 = 1

One variable theorems

Theorem3:

Involution

(x')' = x

Theorem4:

(a) x + (y + z) = (x + y) + z

Associative

(b) x(yz) = (xy)z

(b) (xy)' = x' + y'

2 or 3 variable theorems

Theorem5:

Demorgan

(a) (x + y)' = x'y'

(b) x(x + y) = x

Theorem6:

Absorption

(a) x + xy = x

```

#### Proofs:

(a) The proofs of the theorems with one variable are presented below:

```

THEOREM 1(a): x + x = x

```

| x + x                        | = (x + x) . 1     | (P4: Identity element)     |

|------------------------------|-------------------|----------------------------|

|                              | = (x + x)(x + x') | (P5: Existence of inverse) |

|                              | = x + xx'         | (P3: Distribution)         |

|                              | =x + 0            | (P5: Existence of inverse) |

|                              | =x                | (P4: Identity element)     |

| <b>THEOREM 1(b):</b> x·x = x |                   |                            |

| х.х                          | = xx + 0          | (P4: Identity element)     |

|                              | =xx + xx'         | (P5: Existence of inverse) |

|                              | =x(x + x')        | (P3: Distribution)         |

|                              | = x.1             | (P5: Existence of inverse) |

|                              | =x                | (P4: Identity element)     |

| Have Fach stop in theory     | am 1/h) and 1/a   | ) are dual of each other   |

Hey! Each step in theorem 1(b) and 1(a) are <u>dual</u> of each other.

**THEOREM 2(a):** x + 1 = 1  $x + 1 = 1 \cdot (x + 1)$  (P4: Identity element) = (x + x')(x + 1) (P5: Existence of inverse)  $= x + x' \cdot 1$  (P3: Distribution) = x + x' (P4: Identity element) = 1 (P5: Existence of inverse)

**THEOREM 2(b):** x.0 = 0 by duality.

**THEOREM 3:** (x')' = x. From P5, we have x + x' = 1 and  $x \cdot x' = 0$ , which defines the complement of x. The complement of x' is x and is also (x')'. Therefore, since the complement is unique, we have that (x')' = x.

(b) The theorems involving two or three variables may be proven algebraically from the postulates and the theorems that have already been proven. For example, lets prove <u>Demorgan's theorem</u>:

**THEOREM 5(a):** (x + y)' = x'y'

From postulate P5 (Existence of inverse), for every x in a Boolean algebra there is a unique x' such that

x + x' = 1 and  $x \bullet x' = 0$

Boolean Algebra and Logic Gates

R

So it is sufficient to show that x'y' is the complement of x + y. We'll do this by showing that (x + y) + (x'y') = 1 and  $(x + y) \cdot (x'y') = 0$ .

| (x + y) + (x'y') | = [(x + y) + x'] [(x + y) + y']            | [OR distributes over AND (P3)]                           |

|------------------|--------------------------------------------|----------------------------------------------------------|

|                  | = [(y + x) + x'] [(x + y) + y']            | [OR is commutative (P2)]                                 |

|                  | = [y + (x + x')] [x + (y + y')]            | [OR is associative (Theorem 3(a)), used twice]           |

|                  | = (y + 1)(x + 1)                           | [Complement, x + x' = 1 (P5), twice]                     |

|                  | = 1 • 1                                    | [x + 1 = 1, (Theorem 2), twice]                          |

|                  | = 1                                        | [Idempotent, x • x = x (Theorem 1)]                      |

| Also,            |                                            |                                                          |

| (x + y)(x'y')    | = (x'y') (x + y)                           | [AND is commutative (P2)]                                |

|                  | = [(x'y') x] + [(x'y') y]                  | [AND distributes over OR (P3)]                           |

|                  | = [(y'x')x] + [(x'y')y]                    | [AND is commutative (P2)]                                |

|                  | = [y'(x'x)] + [x'(y'y)]                    | [AND is associative (Theorem 3(b)), twice]               |

|                  | = [y'(xx')] + [x'(yy')]                    | [AND is commutative, twice]                              |

|                  | $= [y' \bullet 0] + [x' \bullet 0]$        | [Complement, $x \bullet x' = 0$ , twice]                 |

|                  | = 0 + 0                                    | [x • 0 = 0, twice]                                       |

|                  | = 0                                        | [ldempotent, x + x = x]                                  |

|                  | A (mall and call a second second structure | least in The second C(s). Cash stee in the second of C(h |

**THEOREM 5(a):**  $(xy)' = x' + y' \leftarrow$  can be proved similarly as in Theorem 5(a). Each step in the proof of 5(b) is the dual of its 5(a) counterparts.

**Hey!** Theorems above can also be proved using truth tables (alternative to algebraic simplification). Viz. theorem 6(a) can be proved as:

| Γ |   |    | · · · · · · |

|---|---|----|-------------|

| x | У | xy | x + xy      |

| 0 | 0 | 0  | 0           |

| 0 | 1 | 0  | 0           |

| 1 | 0 | 0  | 1           |

| 1 | 1 | 1  | 1           |

#### **Operator Precedence**

The operator precedence for evaluating Boolean expressions is

- 1. Parentheses  $\rightarrow$  ()

- 2. NOT→'

- 3. AND  $\rightarrow$ .

- 4. OR→+

In other words, the expression inside the parentheses must be evaluated before all other operations. The next operation that holds precedence is the complement, then follows the AND, and finally the OR. Example: (a+b.c).d'  $\rightarrow$  here we first evaluate 'b.c' and OR it with 'a' followed by ANDing with complement of 'd'.

#### **Boolean Functions**

A Boolean function is an expression formed with binary variables (variables that takes the value of 0 or 1), the two binary operators OR and AND, and unary operator NOT, parentheses, and an equal sign. For given value of the variables, the function can be either 0 or 1.

280

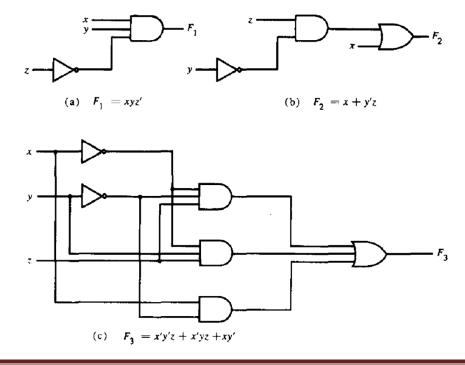

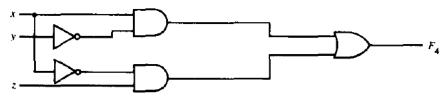

- Boolean function represented as an algebraic expression: Consider Boolean function F<sub>1</sub> = xyz'. Function F is equal to 1 if x=1, y=1 and z=0; otherwise F<sub>1</sub> =0. Other examples are: F<sub>2</sub> = x + y'z, F<sub>3</sub> = x'y'z + x'yz + xy', F<sub>4</sub> = xy' + x'z etc.

- Boolean function represented in a truth table: The number of rows in the truth table is 2<sup>n</sup>, where n is the number of binary variables in the function, The 1's and 0's combinations for each row is easily obtained from the binary numbers by counting from 0 to 2<sup>n</sup> - 1.

| x | У | Z | F <sub>1</sub> | <i>F</i> <sub>2</sub> | F3 | <i>F</i> 4 |

|---|---|---|----------------|-----------------------|----|------------|

| 0 | 0 | 0 | 0              | 0                     | 0  | 0          |

| 0 | 0 | 1 | 0              | 1                     | 1  | 1          |

| 0 | 1 | 0 | 0              | 0                     | 0  | 0          |

| 0 | 1 | 1 | 0              | 0                     | 1  | 1          |

| 1 | 0 | 0 | 0              | 1                     | 1  | 1          |

| 1 | 0 | 1 | 0              | 1                     | 1  | 1          |

| 1 | 1 | 0 | 1              | 1                     | 0  | 0          |

| 1 | 1 | 1 | 0              | 1                     | 0  | 0          |

<u>Million Dollar question</u>: Is it possible to find two algebraic expressions that specify the same function? Answer is: **yes**. Being straightforward, the manipulation of Boolean algebra is applied mostly to the problem of finding simpler expressions for the same function.

Example: Functions  $F_3$  and  $F_4$  are same although they have different combinations of binary variables with in them.

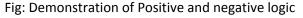

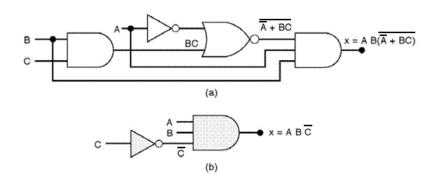

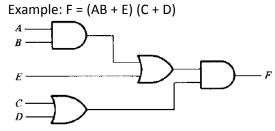

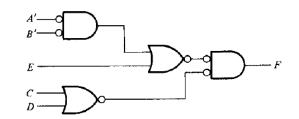

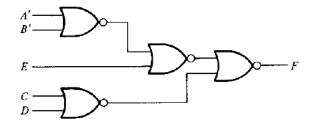

A Boolean function may be transformed from an algebraic expression into a logic diagram composed of AND, OR, and NOT gates. The implementation of the four functions introduced in the previous discussion is shown below:

By Bishnu Rawal

Page 6

$(\mathbf{d}) \quad F_{\mathbf{d}} = xy' + x'z$

Fig: Implementation of Boolean functions with gates

#### Algebraic manipulation and simplification of Boolean function

- A *literal* is a primed or unprimed (i.e. complemented or un-complemented) variable. When a Boolean function is implemented with logic gates, each literal in the function designates an input to a gate, and each *term* is implemented with a gate.

- The **minimization** of the number of literals and the number of terms results in a circuit with less equipment. It is not always possible to minimize both simultaneously; usually, further criteria must be available. At the moment, we shall narrow the minimization criterion to literal minimization. We shall discuss other criteria in unit 3.

- The number of literals in a Boolean function can be minimized by algebraic manipulations. Unfortunately, there are no specific rules to follow that will guarantee the final answer. The only method available is a cut-and-try procedure employing the postulates, the basic theorems, and any other manipulation method that becomes familiar with use. The following examples illustrate this procedure.

$\rightarrow$ Simplify the following Boolean functions to a minimum number of literals.

- 1. x + x'y = (x + x')(x + y) = 1.(x + y) = x + y

- 2. x(x' + y) = xx' + xy = 0 + xy = xy

- 3. x'y'z + x'yz + xy' = x'z(y' + y) + xy = x'z + xy

- 4. xy + x' z + yz = xy + x' z + yz (x + x')

$$= xy + x'z + xyz + x'yz$$

$$= xy(1 + z) + x'z(1 + y)$$

$$= xy + x'z$$

5. (x + y)(x' + z)(y + z) = (x + y)(x' + z) by duality from function 4.

#### **Complement of a function**

The complement of a function F is F' and is obtained from an interchange of 0's for 1's and 1's for 0's in the value of F. The complement of a function may be derived algebraically through DeMorgan's theorem. DeMorgan's theorems can be extended to three or more variables. The three-variable form of the first DeMorgan's theorem is derived below.

| = (A + X)'     | let B + C = X                 |

|----------------|-------------------------------|

| = A'X'         | (DeMorgan)                    |

| = A'· (B + C)' | substitute B + C = X          |

| = A'.(B'C')    | (DeMorgan)                    |

| = A'B'C'       | (associative)                 |

|                | = A'· (B + C)'<br>= A'.(B'C') |

DeMorgan's theorems for any number of variables resemble in form the two variable case and can be derived by successive substitutions similar to the method used in the above derivation. These theorems can be generalized as follows:

(A + B + C + D + ... + F)' = A'B'C'D'... F'(ABCD ... F)' = A' + B' + C' + D' + ... + F'

Page 7

The generalized form of De Morgan's theorem states that the complement of a function is obtained by interchanging AND and OR operators and complementing each literal.

#### Two ways of getting complement of a Boolean function:

1. Applying DeMorgan's theorem:

**Question**: Find the complement of the functions  $F_1 = x'yz' + x'y'z$  and  $F_2 = x(y'z' + yz)$ .  $\rightarrow$  By applying DeMorgan's theorem as many times as necessary, the complements are obtained as follows:

$F_1' = (x'yz' + x'y'z)' = (x'yz')'(x'y'z)' = (x + y' + z)(x + y + z')$

$F_2' = [x(y'z' + yz)]' = x' + (y'z' + yz)' = x' + (y'z')' \cdot (yz)' = x' + (y + z)(y' + z')$

First finding dual of the algebraic expression and complementing each literal Question: Find the complement of the functions F<sub>1</sub> and F<sub>2</sub> of example above by taking their duals and complementing each literal.

- $F_1 = x'yz' + x'y'z$ . The dual of  $F_1$  is (x' + y + z')(x' + y' + z). Complement each literal:  $(x + y' + z)(x + y + z') = F_1'$ .

- $F_2 = x(y'z' + yz)$ . The dual of  $F_1$  is x + (y' + z')(y + z). Complement each literal:  $x' + (y + z)(y' + z') = F_2'$ .

#### **Other logic operations**

When the binary operators AND and OR are placed between two variables, x and y, they form two Boolean functions, x.y and x + y, respectively. There are  $2^{2^n}$  functions for n binary variables. For two variables,  $n^2$ , and the number of possible Boolean functions is 16. Therefore, the AND and OR functions are only two of a total of 16 possible functions. It would be instructive to find the other 14 functions and investigate their properties.

| x   | у      | Fo | F, | <b>F</b> <sub>2</sub> | F3 | F., | F <sub>5</sub> | <i>F</i> <sub>6</sub> | $F_{7}$ | F <sub>8</sub> | _ <b>F</b> 9 | FIO | F11       | F <sub>12</sub> | F13       | F14        | F <sub>15</sub> |

|-----|--------|----|----|-----------------------|----|-----|----------------|-----------------------|---------|----------------|--------------|-----|-----------|-----------------|-----------|------------|-----------------|

|     |        | [  |    |                       |    |     |                |                       |         |                |              |     |           |                 |           |            |                 |

| 0   | 0<br>1 | 0  | 0  | 0                     | 0  | 1   | Ĩ              | 1                     | 1       | 0              | 0            | 0   | Ō         | i               | 1         | 1          | 1               |

| l   | 0<br>1 | 0  | 0  | 1                     | 1  | 0   | 0              | 1                     | 1       | 0              | 0            | 1   | I         | 0               | 0         | 1          | 1               |

| 1   | 1      | 0  | 1  | 0                     | 1  | 0   | 1              | 0                     | 1       | 0              | 1            | 0   | 1         | 0               | 1         | 0          | 1               |

|     | rator  | İ  |    |                       |    |     |                |                       |         |                |              |     |           |                 |           |            |                 |

| syn | nbol   |    |    | 1                     |    | 1   |                | $\oplus$              | +       | ţ              | $\odot$      | ,   | $\subset$ | '               | $\supset$ | $\uparrow$ |                 |

Truth Tables for the 16 Functions of Two Binary Variables

The 16 functions listed in truth table form above can be expressed algebraically by means of Boolean expressions as in following table. Each of the functions is listed with an accompanying name and a comment that explains the function in some way. The 16 functions listed can be subdivided into three categories:

- 1. Two functions that produce a constant 0 or 1.

- 2. Four functions with unary operations: complement and transfer.

- 3. Ten functions with binary operators that define eight different operations: AND, OR, NAND. NOR, exclusive OR, equivalence, inhibition, and implication.

| Boolean functions | Operator<br>symbol | Name         | Comments            |

|-------------------|--------------------|--------------|---------------------|

| $F_0 = 0$         |                    | Null         | Binary constant 0   |

| $F_1 = xy$        | $x \cdot y$        | AND          | x and y             |

| $F_2 = xy'$       | x/y                | Inhibition   | x but not y         |

| $F_3 = x$         |                    | Transfer     | x                   |

| $F_4 = x'y$       | y/x                | Inhibition   | y but not x         |

| $F_5 = y$         |                    | Transfer     | y                   |

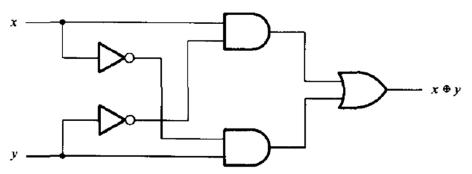

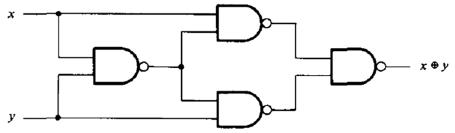

| $F_6 = xy' + x'y$ | $x \oplus y$       | Exclusive-OR | x or y but not both |

| $F_7 = x + y$     | x + y              | OR           | x or y              |

| $F_8 = (x + y)'$  | $x \downarrow y$   | NOR          | Not-OR              |

| $F_9 = xy + x'y'$ | $x \odot y$        | Equivalence  | x equals y          |

| $F_{10} = y'$     | у'                 | Complement   | Not y               |

| $F_{11} = x + y'$ | $x \subset y$      | Implication  | If y then x         |

| $F_{12} = x'$     | <i>x</i> '         | Complement   | Not x               |

| $F_{13} = x' + y$ | $x \supset y$      | Implication  | If $x$ then $y$     |

| $F_{14}=(xy)'$    | $x \uparrow y$     | NAND         | Not-AND             |

| $F_{15} = 1$      |                    | Identity     | Binary constant 1   |

#### Table: Boolean Expressions for the 16 Functions of Two Variables

# **Digital Logic gates (In detail)**

Boolean functions are expressed in terms of AND, OR, and NOT logic operations, and hence are easier to implement with these types of gates. The possibility of constructing gates for the other logic operations is of **practical interest**. Factors to be weighed when considering the construction of other types of logic gates are:

- The feasibility and economy of producing the gate with physical components

- The possibility of extending the gate to more than two inputs

- The basic properties of the binary operator such as commutativity and associativity, and

- The ability of the gate to implement Boolean functions alone or in conjunction with other gates.

Of the 16 functions defined in Table above, two are equal to a constant and four others are repeated twice. There are only ten functions left to be considered as candidates for logic gates. Two, inhibition and implication, are not commutative or associative and thus are impractical to use as standard logic gates. The other eight: **complement**, **transfer**, **AND**, **OR**, **NAND**, **NOR**, **exclusive-OR**, and **equivalence**, are used as standard gates in digital design.

The graphic symbols and truth tables of the eight gates are shown below:

| Name                               | Graphic<br>symbol      | Algebraic<br>function          | Truth<br>table                                                                                           |

|------------------------------------|------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------|

| AND                                | $y = \sum_{y \to F} F$ | F = xy                         | $\begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 0 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \end{array}$ |

| OR                                 |                        | F = x + y                      | $\begin{array}{c ccc} x & y & F \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \end{array}$  |

| Inverter                           |                        | F = x'                         | $\begin{array}{c c} x & F \\ \hline 0 & 1 \\ 1 & 0 \end{array}$                                          |

| Buffer                             |                        | F = x                          | x F<br>0 0<br>1 1                                                                                        |

| NAND                               |                        | F = (xy)'                      | $\begin{array}{c ccc} x & y & F \\ \hline 0 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{array}$  |

| NOR                                |                        | F = (x + y)'                   | $\begin{array}{c ccc} x & y & F \\ \hline 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 0 \end{array}$  |

| Exclusive-OR<br>(XOR)              |                        | $F = xy' + x'y$ $= x \oplus y$ | $\begin{array}{c ccc} x & y & F \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{array}$  |

| Exclusive-NOR<br>or<br>equivalence |                        | $F = xy + x'y'$ $= x \odot y$  | $\begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \end{array}$ |

Fig: listing of eight gates

# **Universal gates**

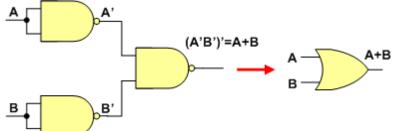

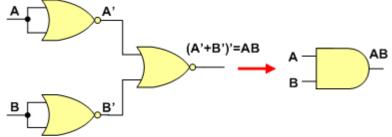

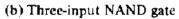

A universal gate is a gate which can implement any Boolean function without need to use any other gate type. The **NAND** and **NOR** gates are universal gates. In practice, this is advantageous since NAND and NOR gates are economical and easier to fabricate and are the basic gates used in all IC digital logic families.

# 1. NAND Gate is a Universal Gate

To prove that any Boolean function can be implemented using only NAND gates, we will show that the AND, OR, and NOT operations can be performed using only these gates.

Implementing an Inverter Using only NAND Gate: All NAND input pins connected to the input signal A gives an output A'.

Implementing AND Using only NAND Gates: The AND is replaced by a NAND gate with its output complemented by a NAND gate inverter.

Implementing OR Using only NAND Gates: The OR gate is replaced by a NAND gate with all its inputs complemented by NAND gate inverters.

Thus, the **NAND gate** is a universal gate since it can implement the AND, OR and NOT functions.

# 2. NOR Gate is a Universal Gate:

To prove that any Boolean function can not be implemented using only NOR gates, we will show that the AND, OR, and NOT operations can be performed using only these gates.

Implementing neither an Inverter Using only NOR Gate: All NOR input pins connect to the input signal A gives an output A'.

Implementing OR Using only NOR Gates: The OR is replaced by a NOR gate with its output complemented by a NOR gate inverter.

Implementing AND Using only NOR Gates: The AND gate is replaced by a NOR gate with all its inputs complemented by NOR gate inverters.

Thus, the **NOR gate** is a universal gate since it can implement the AND, OR and NOT functions.

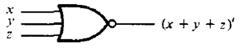

#### Extending gates to multiple inputs

The gates shown in Fig above, except for the inverter and buffer, can be extended to have more than two inputs. A gate can be extended to have multiple inputs if the binary operation it represents is commutative and associative.

- The AND and OR operations, defined in Boolean algebra, possess these two properties. For the OR function, we have x + y = y + x commutative and (x + y) + z = x + (y + z) = x + y + z associative, which indicates that the gate inputs can be interchanged and that the OR function can be extended to three or more variables.

- The NAND and NOR functions are commutative and but not associative  $[x \downarrow (y \downarrow z) \neq (x \downarrow y) \downarrow z]$  $(x \downarrow y) \downarrow z = [(x + y)' + z]' = (x + y)z' = xz' + yz'$

$$x \downarrow (y \downarrow z) = [x + (y + z)']' = x'(y + z) = x'y + x'z$$

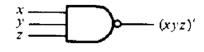

Their gates can be extended to have more than two inputs, provided the definition of the operation is slightly modified. We define the multiple NOR (or NAND) gate as a complemented OR (or AND) gate i.e.  $x \downarrow y \downarrow z = (x + y + z)'$  and  $x \uparrow y \uparrow z = (xyz)'$ .

(a) Three-input NOR gate

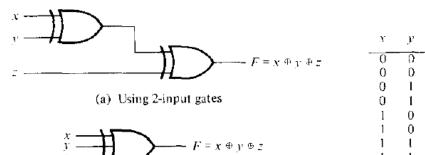

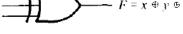

• The exclusive-OR and equivalence gates are both commutative and associative and can be extended to more than two inputs

(b) 3-input gate

Fig: 3-input XOR gate

By Bishnu Rawal

# IC digital logic Families

Continuing the introduction of integrated Circuits (Chips) in unit 1, I will introduce u guys different logic families along with their characteristics.

# **Digital logic families**

Digital logic family refers to the specific circuit technology to which digital integrated circuits belong. Family has its own basic electronic circuit upon which more complex digital circuits and components are developed. The basic circuit in each technology is a NAND, NOR, or an inverter gate. The electronic components used in the construction of the basic circuit are usually used as the name of the technology. Different logic families have been introduced commercially. Some of most popular are:

- TTL (transistor-transistor logic): The TTL family evolved from a previous technology that used diodes and transistors for the basic NAND gate. This technology was called DTL for diodetransistor logic. Later the diodes were replaced by transistors to improve the circuit operation and the name of the logic family was changed to TTL.

- ECL (emitter-coupled logic): Emitter-coupled logic (ECL) circuits provide the highest speed among the integrated digital logic families. ECL is used in systems such as supercomputers and signal processors, where high speed is essential. The transistors in ECL gates operate in a nonsaturated state, a condition that allows the achievement of propagation delays of 1 to 2 nanoseconds.

- MOS (metal-oxide semiconductor): The metal-oxide semiconductor (MOS) is a unipolar transistor that depends upon the flow of only one type of carrier, which may be electrons (nchannel) or holes (p-channel), this is in contrast to the bipolar transistor used in TTL and ECL gates, where both carriers exist during normal operation. A p-channel MOS is referred to as PMOS and an n-channel as NMOS. NMOS is the one that is commonly used in circuits with only one type of MOS transistor.

- **CMOS** (complementary metal-oxide semiconductor): Complementary MOS (CMOS) technology uses one PMOS and one NMOS transistor connected in a complementary fashion in all circuits. The most important advantages of MOS over bipolar transistors are the high packing density of circuits, a simpler processing technique during fabrication, and a more economical operation because of the low power consumption.

- **IIL (Integrated Injection Logic):** Integrated injection logic (**IIL**, **I**<sup>2</sup>**L**, or **I2L**) is a class of digital circuit technology built with multiple collector bipolar junction transistors (BJT). When introduced it had speed comparable to TTL yet was almost as low power as CMOS, making it ideal for use in VLSI (and larger) integrated circuits. Although the logic voltage levels are very close (High: 0.7V, Low: 0.2V), I<sup>2</sup>L has high noise immunity because it operates by current instead of voltage. Sometimes also known as Merged Transistor Logic.

Currently, silicon-based Complementary Metal Oxide Semiconductor (CMOS) technology dominates due to its high circuit density, high performance, and low power consumption. Alternative technologies based on Gallium Arsenide (GaAs) and Silicon Germanium (SiGe) are used selectively for very high speed circuits.

# **Characteristics of digital logic families (Technology Parameters)**

For each specific implementation technology, there are details that differ in their electronic circuit design and circuit parameters. The most important parameters used to characterize an implementation technology are: 599

#### 1. Fan-in

For high-speed technologies, *fan-in*, the number of inputs to a gate, is often restricted on gate primitives to no more than four or five. This is primarily due to electronic considerations related to gate speed. To build gates with larger fan-in, interconnected gates with lower fan-in are used during technology mapping. A mapping for a 7-input NAND gate is made up of two 4- input NANOs and an inverter as shown in figure.

Fig: Implementation of a 7-input NAND Gate using NAND Gates with 4 or Fewer Inputs.

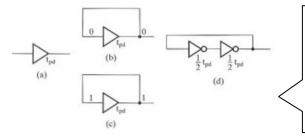

#### 2. Propagation delay

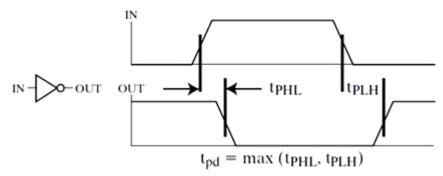

The signals through a gate take a certain amount of time to propagate from the inputs to the output. This interval of time is defined as the **propagation delay of the gate**. Propagation delay is measured in nanoseconds (ns). 1 ns is equal to  $10^{-9}$  of a second. The signals that travel from the inputs of a digital circuit to its outputs pass through a series of gates. The sum of the propagation delays through the gates is the total delay of the circuit.

The average propagation delay time of a gate is calculated from the input and output waveforms as:

Fig: Measurement of propagation delay

- Delay is usually measured at the 50% point with respect to the H and L output voltage levels.

- High-to-low (t<sub>PHL</sub>) and low-to-high (t<sub>PLH</sub>) output signal changes may have different propagation delays.

- High-to-low (HL) and low-to-high (LH) transitions are defined with respect to the output, **not the input**.

- An HL input transition causes:

- an LH output transition if the gate inverts and

- An HL output transition if the gate does not invert.

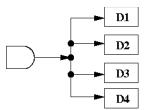

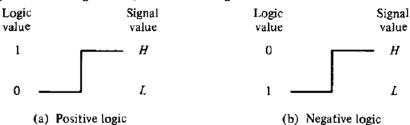

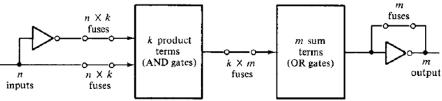

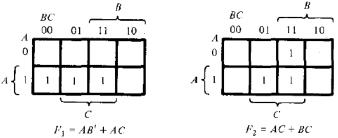

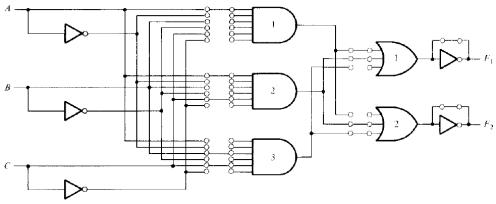

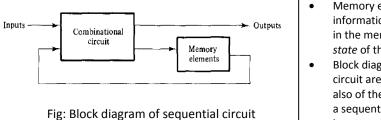

#### 3. Fan-out